4321 Inverter

Published:

Take a read of Shepard’s Online CAD Tutorial. It’s a pretty comprehensive guide, but if you follow it blindly into your project, for sure you will get in trouble! Below, we’ll go through the process systematically and highlight common pitfalls so you can avoid a massive learning curve.

Layout

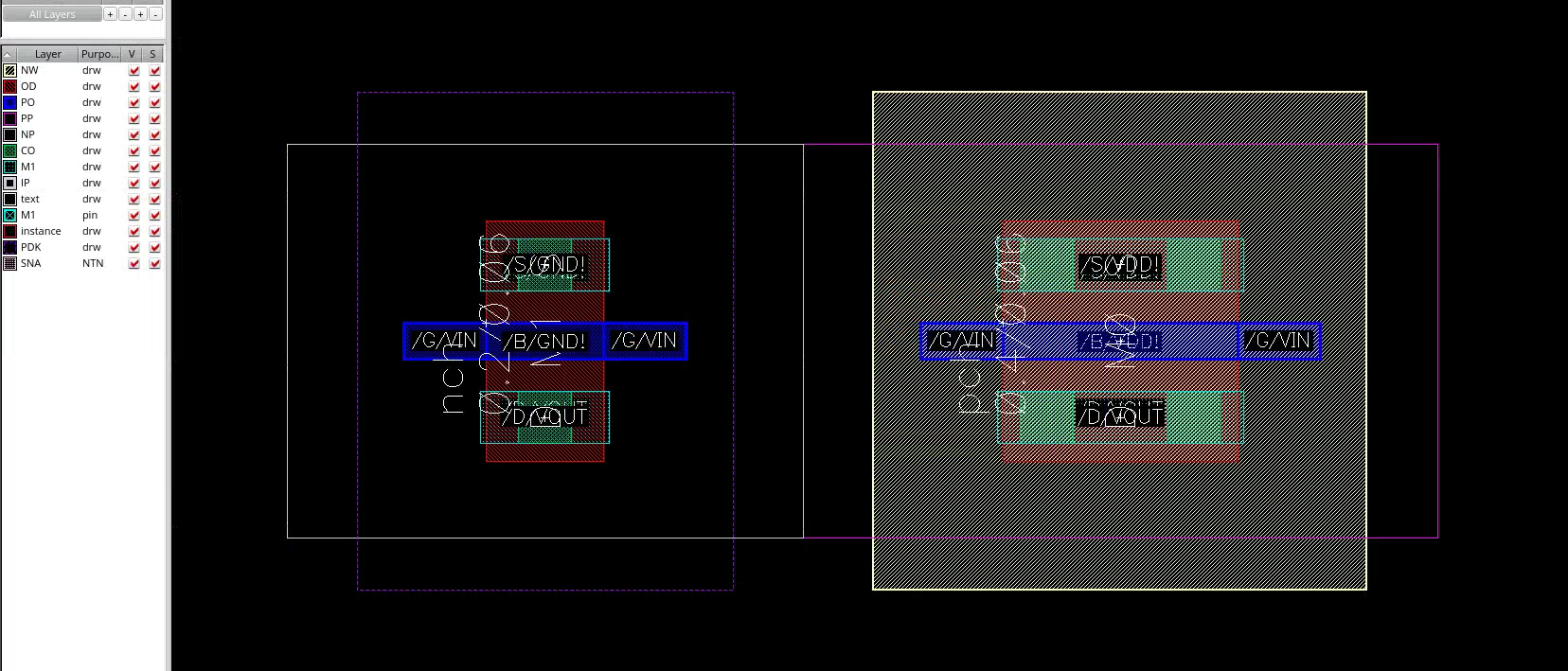

1. Generate All From Source

- Create a new “Layout” the same name as your schematic

- Go to “Connectivity/Generate/All From Source”. You will get two transistors, and a few cyan (M1) Pins

- You should see matching instances between schematic and layout. Selecting one highlights the other.

- Ignore the Pins for now

- Rotate the devices by 90 degrees.

- Align the transistors

- Make sure

NPandPPboundaries perfectly align. No gaps or overlaps

- Make sure

Layers

Before drawing, it’s important to understand the layers we have:

You can double click on a layer to make it exclusively visible, and inspect each layer individually

MOSFET

A MOSFET is a piece of silicon with 4 terminals: Gate, Source, Drain, and Body. S and D are typically symmetrical.

Body

NW(N-Well): where PMOS sitsSUB(P-Well, SUBstrate): where NMOS sits- Marked by

PDK

- Marked by

Source/Drain (diffusion)

OD(Oxide Diffusion): source and drainPP(P imPlant mask,pimp)PP∩OD: p+ diffusion

NP(N imPlant mask)NP∩OD: n+ diffusion

Gate

PO(POlysillicon)

Metal

Now we need to connect metal wires to the devices

CO(COntact, Ohmic): connectsPO/OD(silicon) withM1(metal)M1: First Metal layerVIA1: connectsM1andM2M2: Second Metal layerVIA2: connectsM2andM3- and so on…

Pin

Used to label connections across hierarchies. Nothing electrical.

If you are interested in the physical implementation of these layers, this article explains in glorious detail

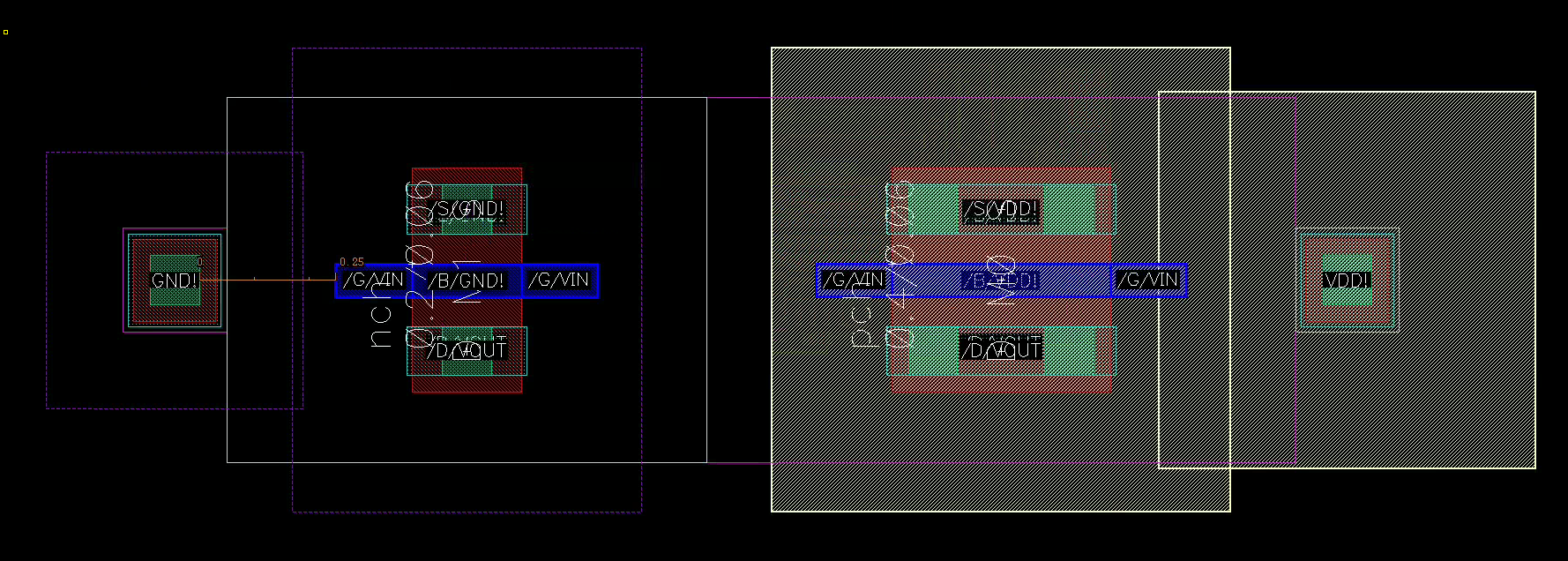

2. Body Vias

Next, add Body Vias. Click o to add M1-SUB and M1-NW Vias.

- Again, make sure

NPandPPboundaries perfectly overlap.

The Body contacts are nothing special: simply a stack of 5 layers connecting Body to Metal:

NW(P) / substrate (N)NP(P) /PP(N)ODCOM1

“Detached Body” creates Body contacts explicitly. Not needed if you’ve used Body Vias

A Body Via can power a large region of P/N substrate (~30 um)

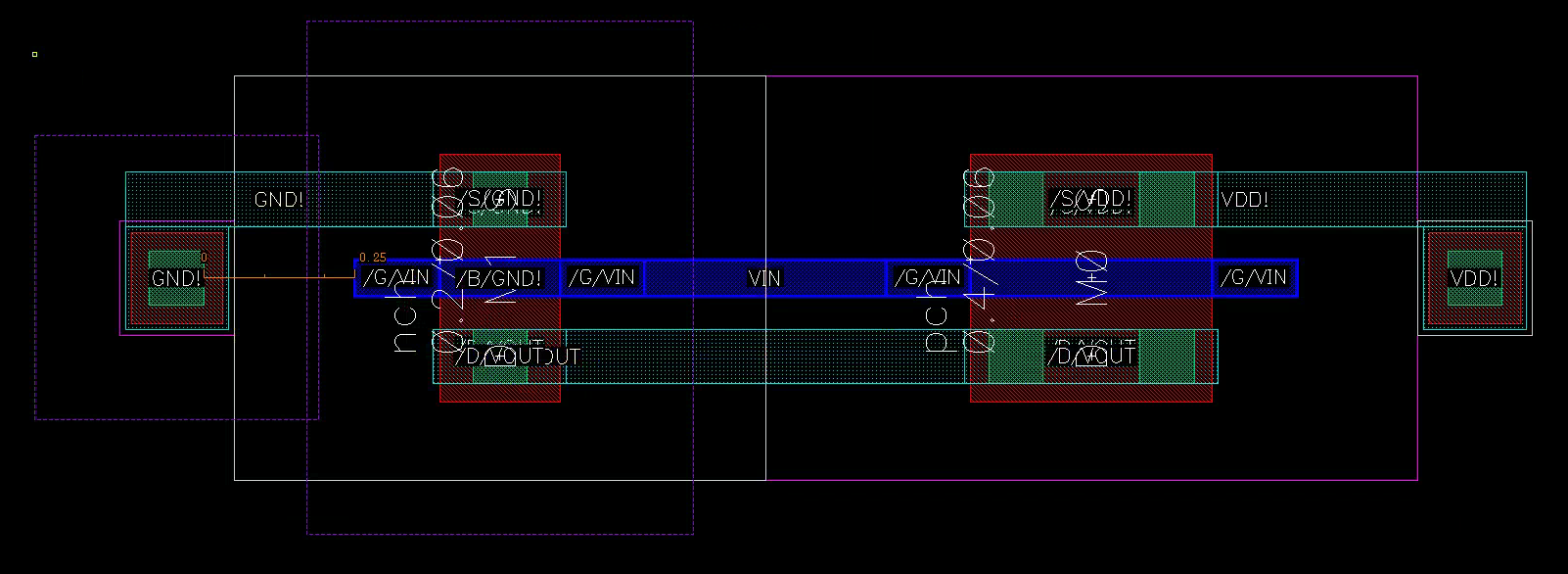

3. Connections

Now let’s connect the PO gate and M1 source/drain to complete the circuit:

DRC

Run DRC as frequently as possible, especially if you are a beginner!!

Skip to Shepard’s Calibre DRC tutorial and set up the environment

These are the main types of DRC errors for TSMC N65:

- Shape rules

- Shapes must satisfy a minimum area

- Shapes must have a minimum width

- Shapes must also meet constraints, such as a minimum side length

- Inter-shape rules

- Enclosure: for example, a Via must be properly enclosed by its associated Metal layers

- Sometimes, minimum overlap or enclosure area also apply.

- Spacing: minimum spacing must be maintained

- between shapes of the same layer, and

- between shapes on different layers, such as spacing to body connections

- Enclosure: for example, a Via must be properly enclosed by its associated Metal layers

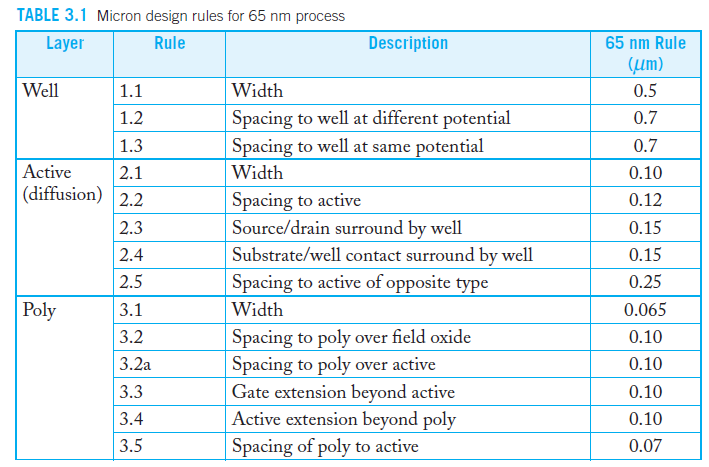

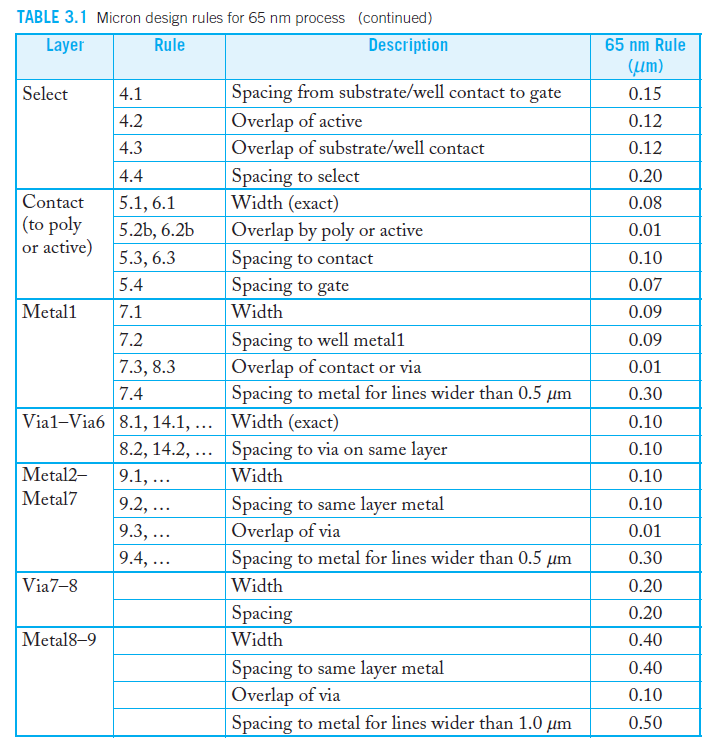

Here’s a (simplified) list from textbook pages 118-119

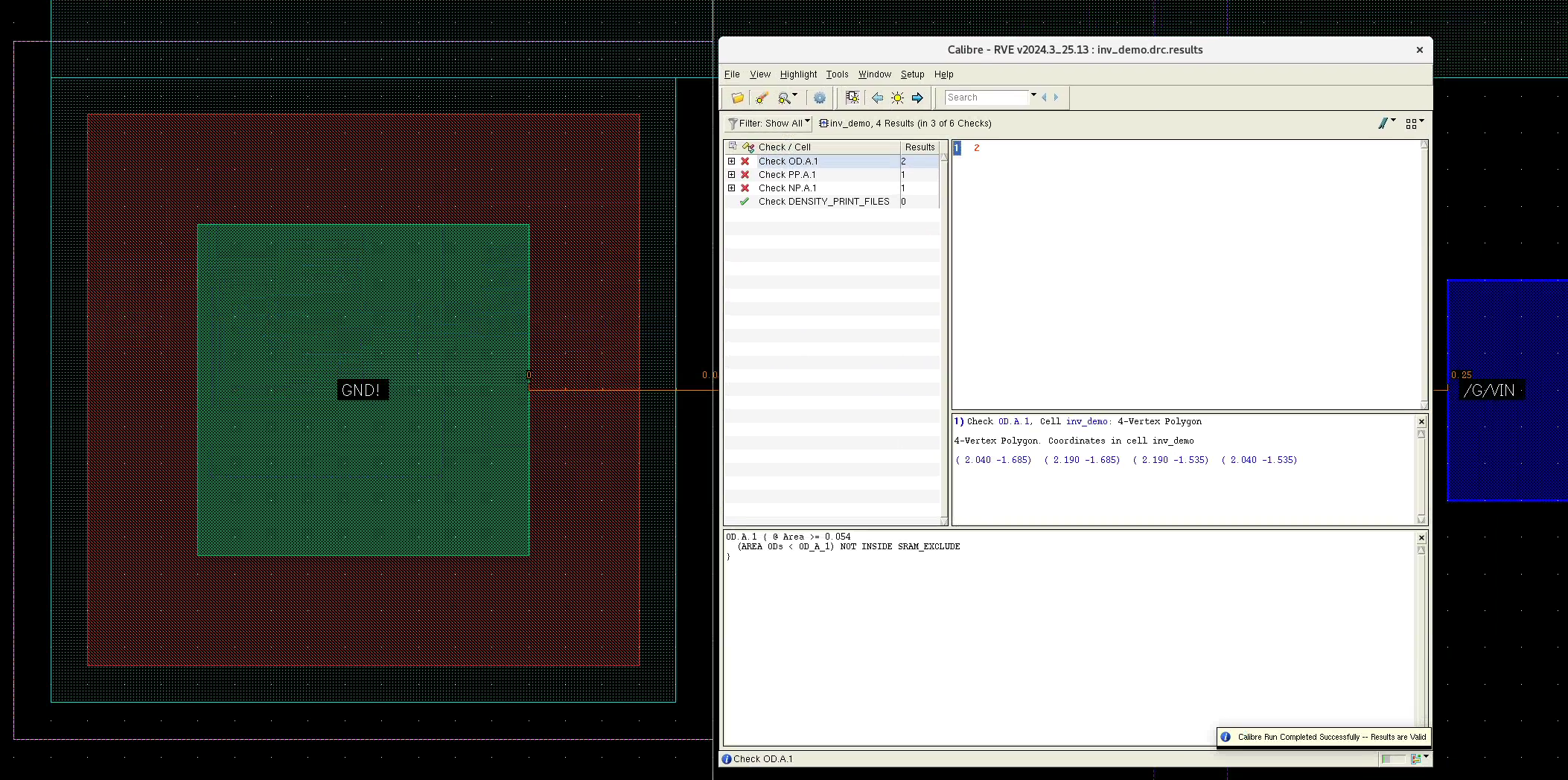

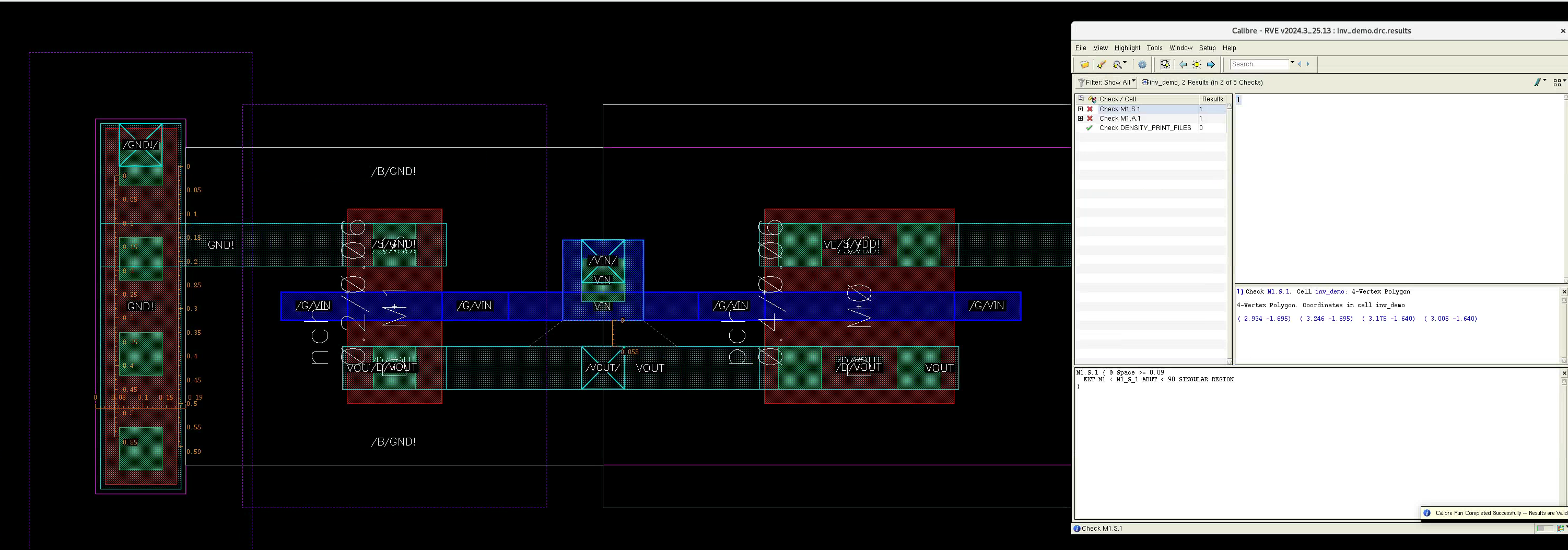

Let’s run a DRC right now

RIP, got 4 errors. You should be grateful that we only got 4…

2 each for the N and P body vias

ODlayer area too smallPP/NPlayer area too small.

There are two ways to solve it:

- Increase via rows/columns

- This is simple. Changing it to 4 will work

- Manually draw a larger

OD/PP/NParound the current layer- This is more risky, as changing one layer may violate other spacing/enclosure rules

- but useful for aggressive optimizations, as you will see later

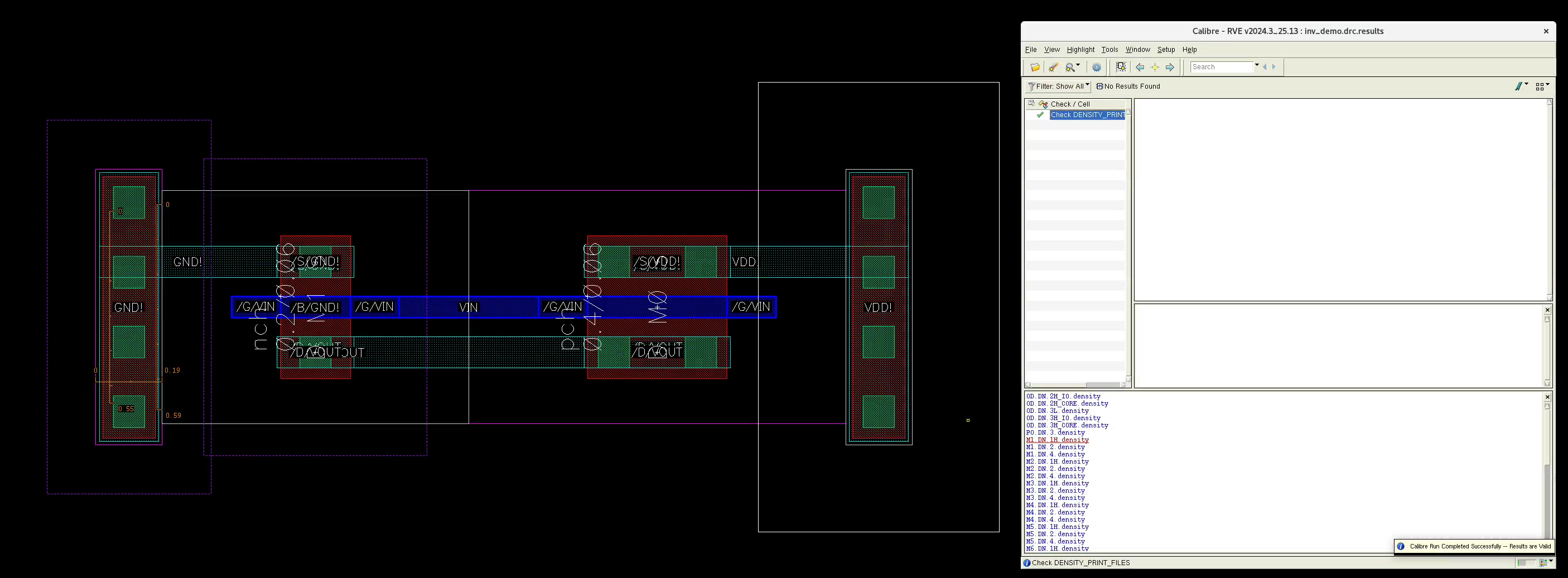

After fixing them and making sure the area rules are satisfied, we are now DRC clean!

4. Gate Via

There’s one more step to connect a wire from our silicon Poly. Add a M1-PO via.

Similar to the Body Vias, this M1-PO also has layers:

POCOM1

All layers must satisfy DRC rules.

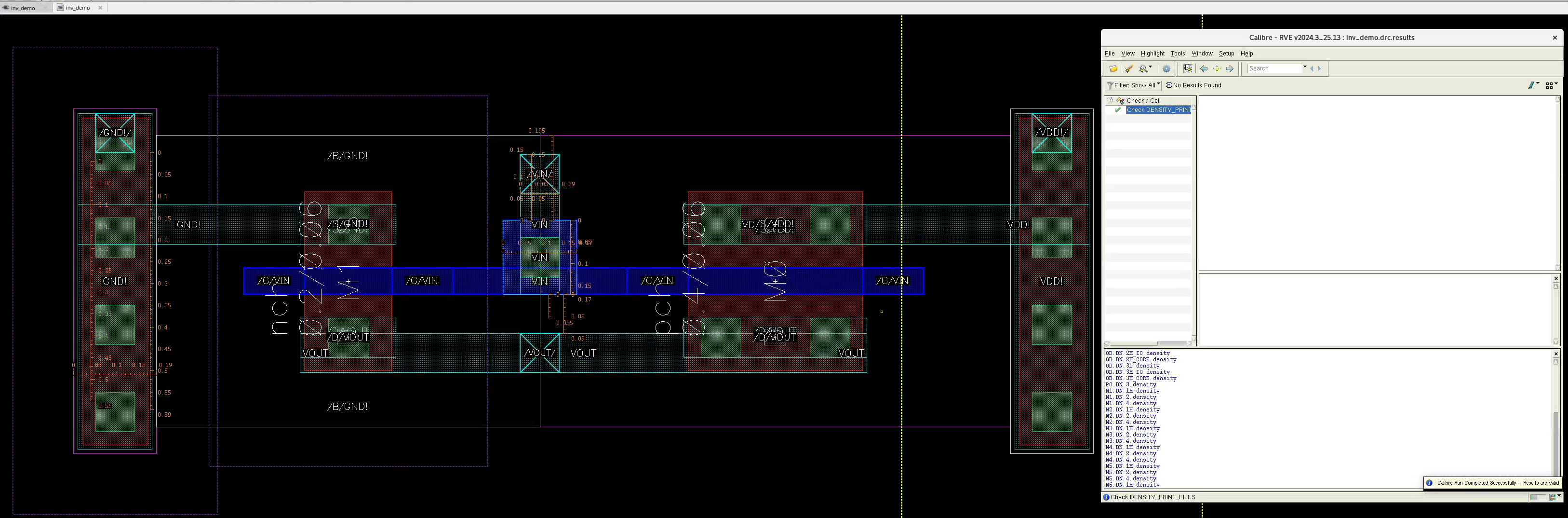

Now run a DRC:

RIP, another two violations. Make only M1 visible for more clarity

M1of the via is too close with our VOUTM1.- Fix: Move either one away to at least 0.09 um apart

M1of the via’s area is too small. It’s like an island- Fix: Add more

M1to the via so its area is more than 0.042 um²

- Fix: Add more

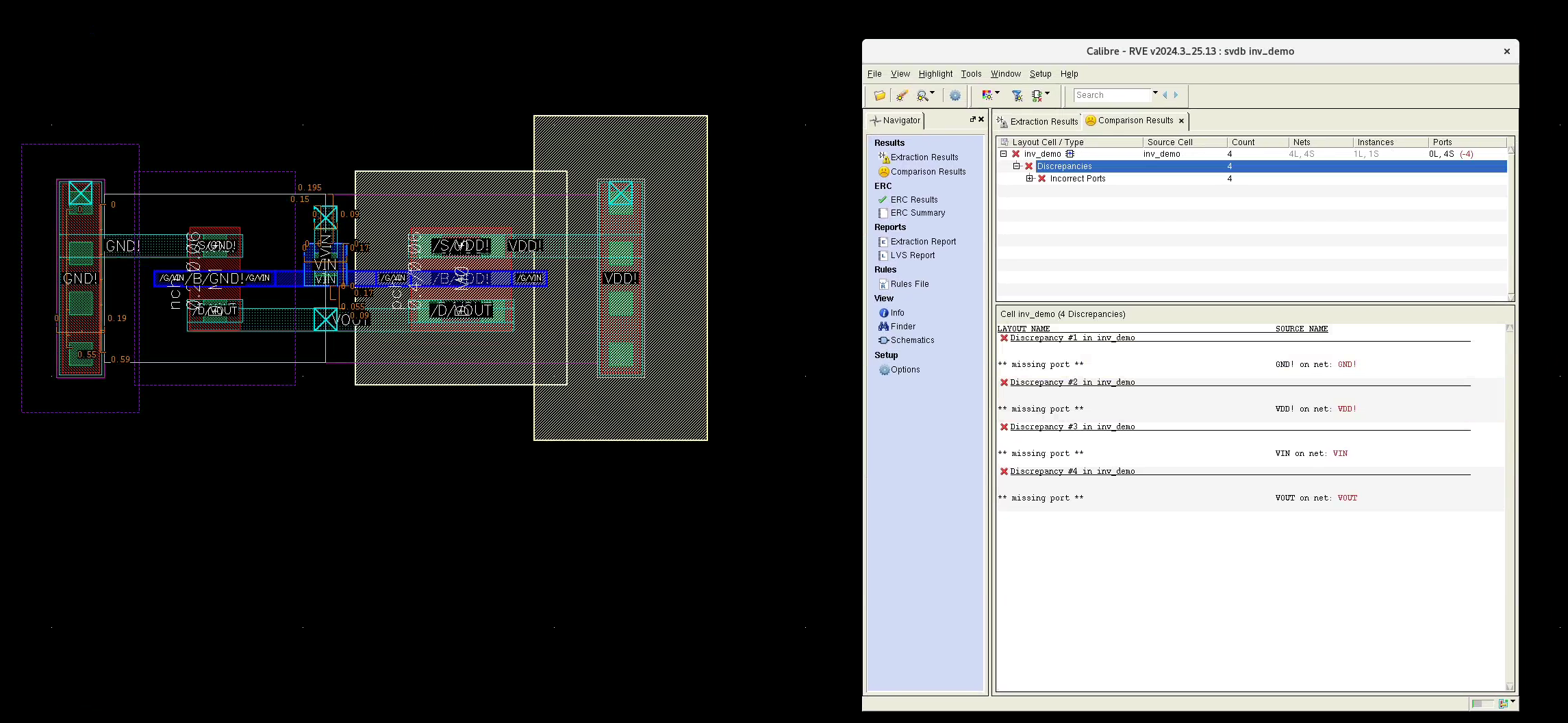

LVS

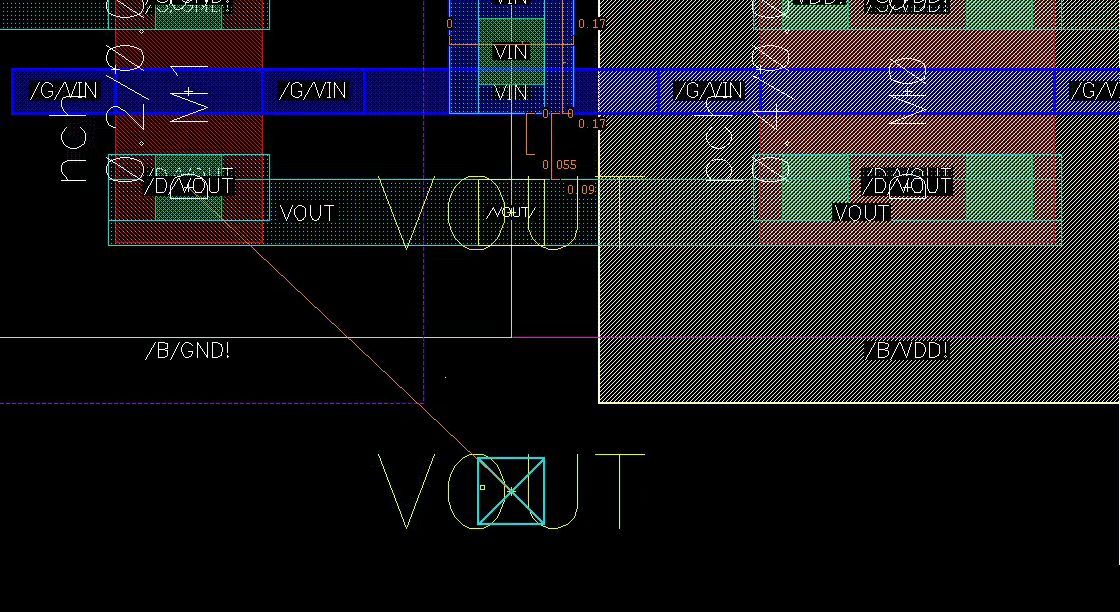

Move the Generated M1 Pins over to the metals.

Check LVS. Read the tutorial for the setup

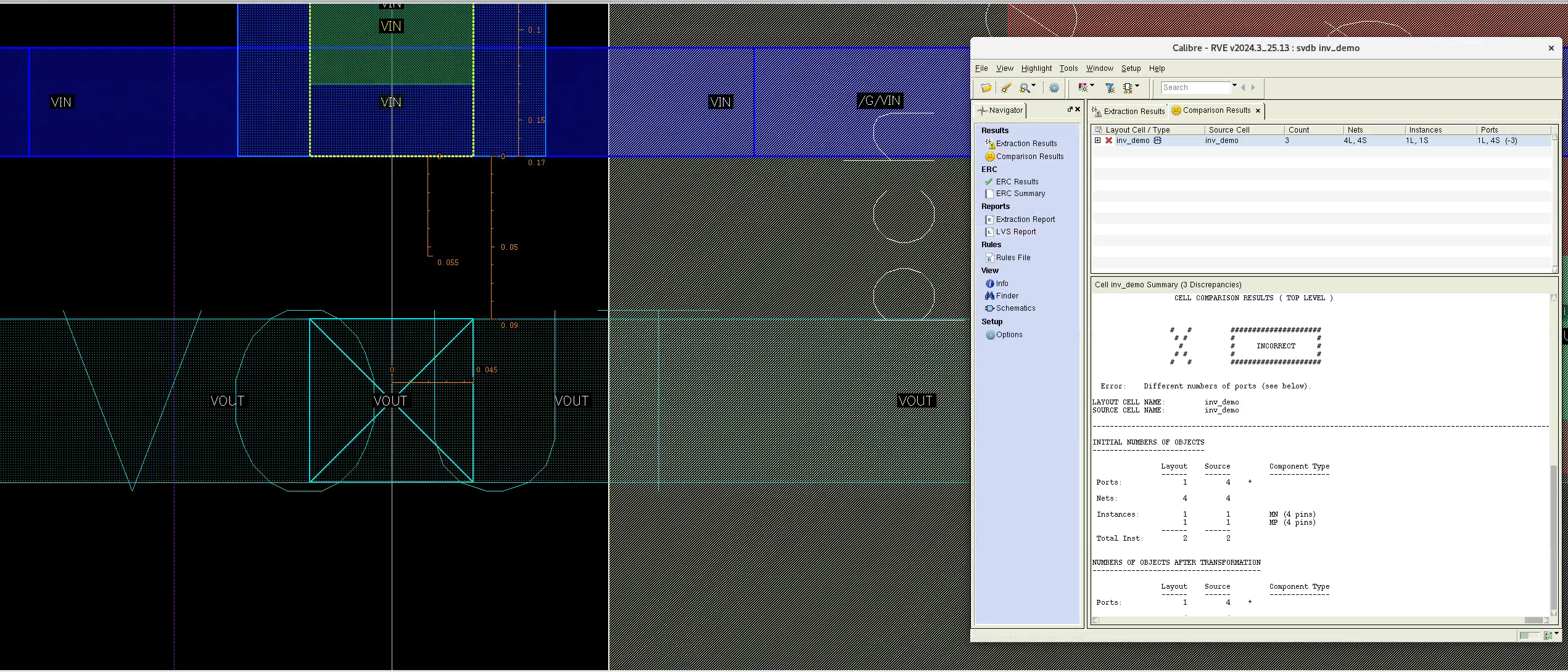

RIP, we got 4 “Incorrect Ports” errors. LVS somehow does not recognize our pins and decide, despite they are created with labels! This is very rare…

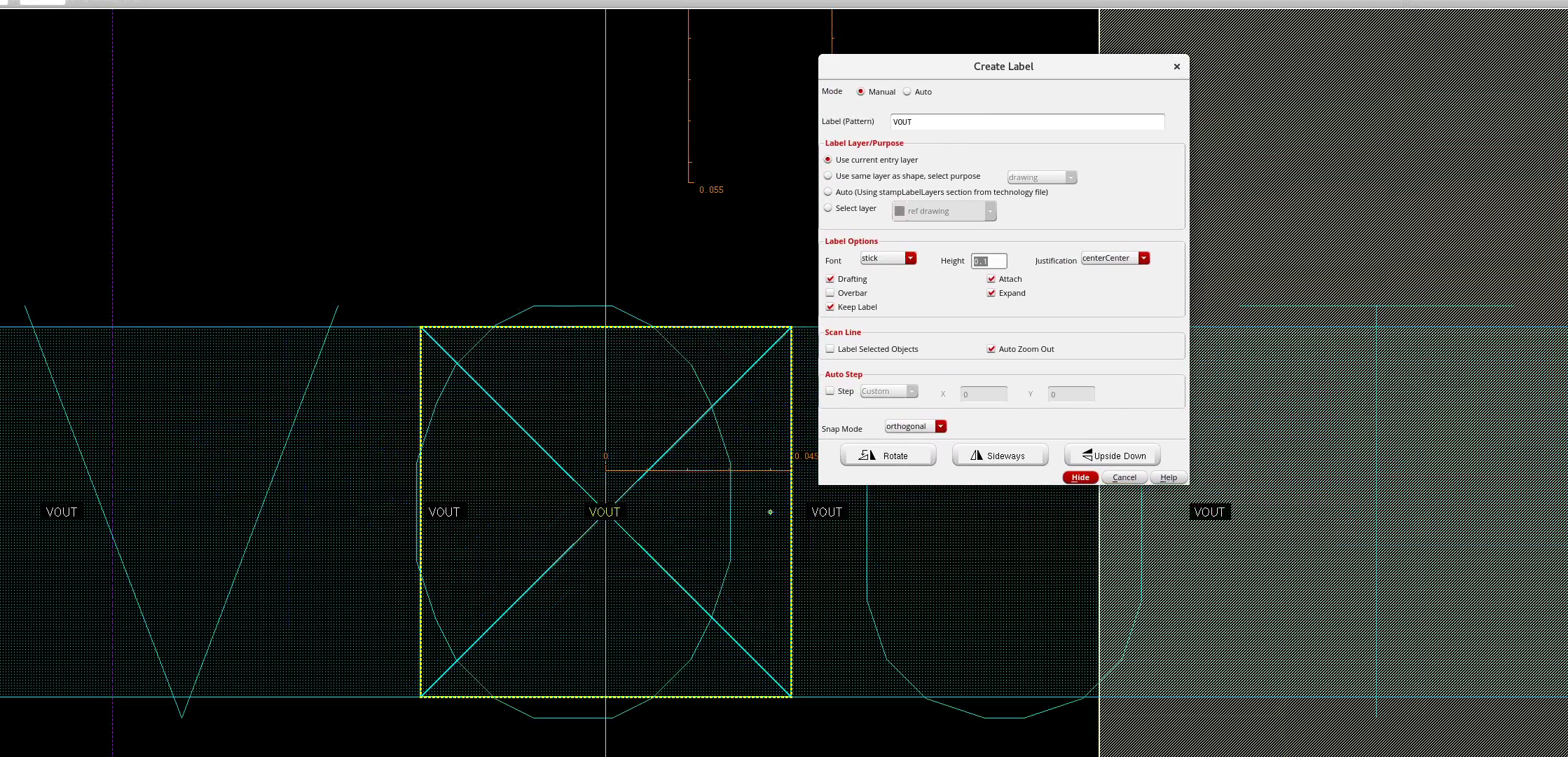

In this case, first check if Virtuoso recognizes the pin. Try moving the pins around and see if the label (“VOUT”) and the cross shows up. If not, delete the pins and “Connectivity/Update/All from Source” again. Make sure you select the “Create Label” option

Here, we do have everything, let’s manually add the labels to the pins again to let LVS know.

- Click

land create label “VOUT”. - Click the center of your pin

- Choose “Purpose”: “pin” as the object

Now, as a proof of concept, run LVS again to see if the error count drops to 3

Yep, so add labels to the other three, and you will be LVS clean!

Virtuoso FAQ

When I open Virtuoso, all my instances show up as red boxes

Click Shift+F to display instances, and Ctrl+F to hide them

My pins do not have labels on them (or LVS doesn’t recognize them)

In “I/O Pins”, you have to set “Pin Label/Create Label As/Label”. Set:

- “Font Height”: 0.1 (recommended)

- “Layer Name”: “Same As Pin”

- “Layer Purpose”: “Same As Pin”

Cadence keyboard shortcuts stopped responding

Stacked functions. Close unused tabs, and press ESC to quit current functions

My layout nets are not showing up

Open with Layout XL